# **VT82C580VP**

# **APOLLO VP**

# Green Pentium/P54C/M1/K5 PCI/ISA System with Unified Memory Architecture, Universal Serial Bus and Master Mode PCI-IDE Controller

DATE : February, 1996

# VIA TECHNOLOGIES, INC.

This datasheet has been downloaded from http://www.digchip.com at this page

# **Copyright Notice:**

Copyright © 1995, 1996 Via Technologies Incorporated. Printed in Taiwan. ALL RIGHTS RESERVED.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of Via Technologies Incorporated.

The VT82C580VP, VT82C585VP, VT82C586 and VT82C587VP may only be used to identify products of VIA Technologies.

PS/2<sup>™</sup> is a registered trademark of International Business Machines Corp.

Pentium<sup>™</sup>, and P54C<sup>™</sup> are registered trademarks of Intel Corp.

M1<sup>™</sup> is a registered trademark of Cyrix Corp.

K86<sup>™</sup> (K5) is a registered trademark of Advanced Micro Devices Corp.

Windows 95<sup>™</sup> and Plug and Play<sup>™</sup> are registered trademarks of Microsoft Corp.

PCI<sup>™</sup> is a registered trademark of the PCI Special Interest Group.

Cache<sup>™</sup> is a registered trademark of Mosys Inc.

All trademarks are the properties of their respective owners.

# **Disclaimer Notice:**

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided by this document is believed to be accurate and reliable to the publication date of this document. However, VIA Technologies assumes no responsibility for any errors in this document. Furthermore, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

## **Offices:**

5020 Brandin Court

8th Floor, No. 533

Fremont, CA

94538

USA

Chung-Cheng Rd., Hsin-Tien

Tel:

(510) 683-3300

Fax:

(510) 683-3301

### **REVISION HISTORY**

| Document<br>Release | Revision            | Date     |

|---------------------|---------------------|----------|

|                     | Revision 1.0        | 2/15/96  |

|                     | Preliminary Release | 10/25/95 |

# **Table of Contents**

| Features                               | 1  |

|----------------------------------------|----|

| Overview                               | 4  |

| Configuration Register of VT82C580VP   | 7  |

| VT82C585VP (Host -PCI)                 | 7  |

| VT82C586 (PCI-ISA/IDE/USB)             | 16 |

| AC Timing Characteristics              | 33 |

| VT82C580VP Pin Description             | 51 |

| Electrical Characteristics             | 67 |

| VT82C580VP Packages                    | 68 |

| Appendix A: Schematics                 |    |

| Appendix B: Operating Guide of VT5063B |    |

| Appendix C: Performance of VT82C580VP  |    |

## VIA VT82C580VP APOLLO-VP PENTIUM/P54C PCI/ISA GREEN PC SYSTEMS WITH UNIFIED MEMORY ARCHITECTURE, UNIVERSAL SERIAL BUS AND MASTER MODE PCI-IDE CONTROLLER

### **F**EATURES

\* PCI/ISA Green PC Ready

#### \* High Integration

- VT82C585VP system controller

- VT82C586 PCI to ISA bridge

- Two instances of the VT82C587VP data buffers

- Six TTLs for a complete main board implementation

#### \* Flexible CPU Interface

- 64-bit P54C<sup>TM</sup>, K5<sup>TM</sup> and M1<sup>TM</sup> CPU interface

- CPU external bus speed up to 66Mhz (internal 200Mhz and above)

- Supports CPU internal write-back cache

- Concurrent CPU/cache and PCI/DRAM operation

- System management interrupt, memory remap and STPCLK mechanism

- Cyril M1 linear burst support

- CPU NA#/Address pipeline capability

#### \* Advanced Cache Controller

- Direct map write back or write through secondary cache

- Burst Synchronous (Pipelined or non-pipelined), asynchronous SRAM, and Cache Module support

- Eight-pin CWE# and GWE# control options

- Flexible cache size: 0K/256K/512K/1M/2MB

- 32 byte line size to match the primary cache

- Integrated 10-bit tag comparator

- 3-1-1-1 read/write timing for Burst Synchronous SRAM access at 66Mhz

- 3-1-1-1-1-1 back to back read timing for Burst Synchronous SRAM access at 66Mhz

- Sustained 3 cycle write access for Burst Synchronous SRAM access or CPU to DRAM and PCI bus

post write buffers at 66Mhz

- 3-2-2 (read) and 4-2-2-2 (write) timing for interleaved asynchronous SRAM access at 66Mhz

- Data streaming for simultaneous primary and secondary cache line fill

- System and video BIOS cacheable and write-protect

- Programmable cacheable region and cache timing

- Optional combined tag and alter bit SRAM for write-back scheme

#### \* Fast DRAM Controller

- Concurrent DRAM writeback

- Four Cache lines (16 quadwords) of CPU/cache to DRAM write buffers

- Fast Page Mode/EDO/Burst EDO/Synchronous-DRAM support in a mixed combination

- Mixed 256K/512K/1M/2M/4M/8M/16MxN DRAMs

- 6 banks up to 512MB DRAMs (maximum four banks of Synchronous DRAM)

- Flexible row and column addresses

- 64 bit or 32 bit data width in arbitrary mixed combination

- 3.3v and 5v DRAM without external transceivers

- Speculative DRAM access

- Read around Write capability for non-stalled CPU read

- Burst read and write operation

- 4-2-2-2 on page, 7-2-2-2 start page and 9-2-2-2 off page timing for EDO DRAMs at 50/60Mhz

- 4-2-2-2 on page, 8-2-2-2 start page and 11-2-2-2 off page timing for EDO DRAMs at 66Mhz

- 5-1-1-1 on page, 8-1-1-1 start page and 10-1-1-1 off page timing for Burst EDO DRAMs at 66Mhz

- 5-2-2-3-1-2-2 back-to-back access for EDO DRAM at 66Mhz

- 5-1-1-3-1-1-1 back-to-back access for BEDO DRAM at 66Mhz

- BIOS shadow at 16KB increment

- System management memory remapping

- Decoupled and burst DRAM refresh with staggered RAS timing

- Programmable refresh rate, CAS-before-RAS refresh and refresh on populated banks only

#### \* Unified Memory Architecture

- Supports VESA UMA handshake protocol

- Compatible with major video/GUI products

- Direct video frame buffer access

- Satisfies maximum latency requirement from REQ# to GNT# and from GNT# to REQ#

#### \* Intelligent PCI Bus Controller

- 32 bit PCI interface

- Supports 66Mhz and 3.3v/5v PCI bus

- PCI master snoop ahead and snoop filtering

- PCI master Peer Concurrency

- Synchronous Bus to CPU clock with divide-by-two from the CPU clock

- Automatic detection of data streaming burst cycles from CPU to the PCI bus

- Five levels (double-words) of CPU to PCI posted write buffers

- Byte merging in the write buffers to reduce the number of PCI cycles and to create further PCI bursting possibilities

- Zero wait state PCI master and slave burst transfer rate

- PCI to system memory data streaming up to 132Mbyte/sec

- Sixty-four levels (double-words) of post write buffers from PCI masters to DRAM

- Thirty-two levels (double-words) of prefetch buffers from DRAM for access by PCI masters

- Enhanced PCI command optimization (MRL, MRM, MWI, etc)

- Complete steerable PCI interrupts

- Supports L1 write-back forward to PCI master read to minimize PCI read latency

- Supports L1 write-back merged with PCI master post-write to minimize DRAM utilization

- Provides transaction timer to fairly arbitrate between PCI masters

- PCI-2.1 compliant

#### \* Enhanced Master Mode PCI IDE Controller

- Dual channel master mode PCI supporting four Enhanced IDE devices

- Transfer rate up to 22MB/sec to cover PIO mode 4 and Multiword DMA mode 2 drivers and beyond

- Sixteen levels (doublewords) of prefetch and write buffers

- Interlaced commands between two channels

- Bus master programming interface for ATA controllers SFF-8038 rev.1.0 compliant

- Full scatter and gather capability

- Support ATAPI compliant devices

- Support PCI native and ATA compatibility modes

- Complete software driver support

#### \* Universal Serial Bus Controller

- USB v1.0 and Intel Universal HCI v1.0 compatible

- Eighteen levels(doublwords) of data FIFOs

- Root hub and two function parts with built-in physical layer transceivers

- Legacy keyboard and PS/2 mouse support

#### \* Plug and Play Controller

- Dual interrupt and DMA signal steering with plug and play control

- − Microsoft Windows 95<sup>TM</sup> and plug and play BIOS compliant

#### \* Sophisticated Power Management Unit

- Normal, doze, sleep, suspend and conserve modes

- System event monitoring with two event classes

- One idle timer, one peripheral timer and one general purpose timer

- More than ten general purpose Input/Output ports

- Six external event input ports with programmable SMI condition

- Complete leakage control when external component is in power off state

- Primary and secondary interrupt differentiation for individual channels

- Clock stretching, clock throttling and clock stop control

- Multiple internal and external SMI sources for flexible power management models

- Two programmable output ports

- APM 1.1 compliant

#### \* PCI to ISA Bridge

- Integrated 82C206 peripheral controller

- Integrated keyboard controller with PS2 mouse supports

- Integrated DS12885 style real time clock with extended 128 byte CMOS RAM

- Integrated USB (universal serial bus) controller with hub and two function ports

- Integrated master mode enhanced IDE controller with enhanced PCI bus commands

- PCI-2.1 compliant with delay transaction

- Four double-word line buffer between PCI and ISA bus

- Supports type F DMA transfers

- Fast reset and Gate A20 operation

- Edge trigger or level sensitive interrupt

- Flash EPROM and combined BIOS support

- \* Built-in nand-tree pin scan test capability

- \* 0.6um mixed voltage, high speed and low power CMOS process

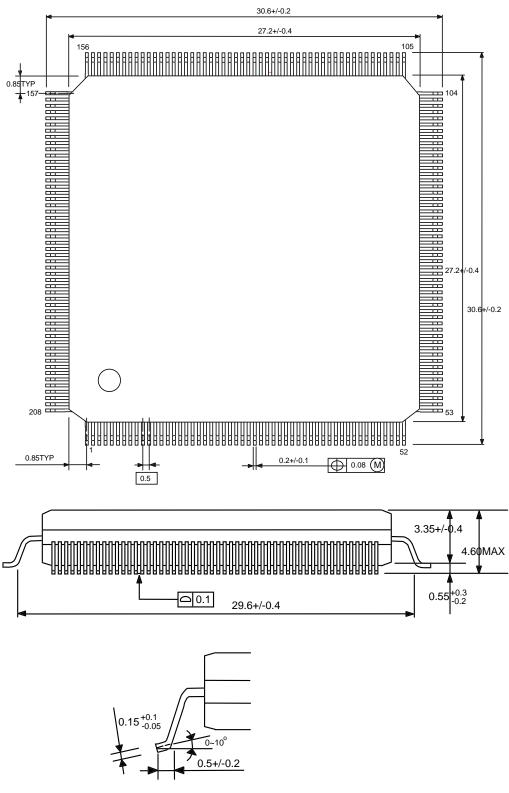

- \* 208 pin PQFP for VT82C585VP

- \* 208 pin PQFP for VT82C586

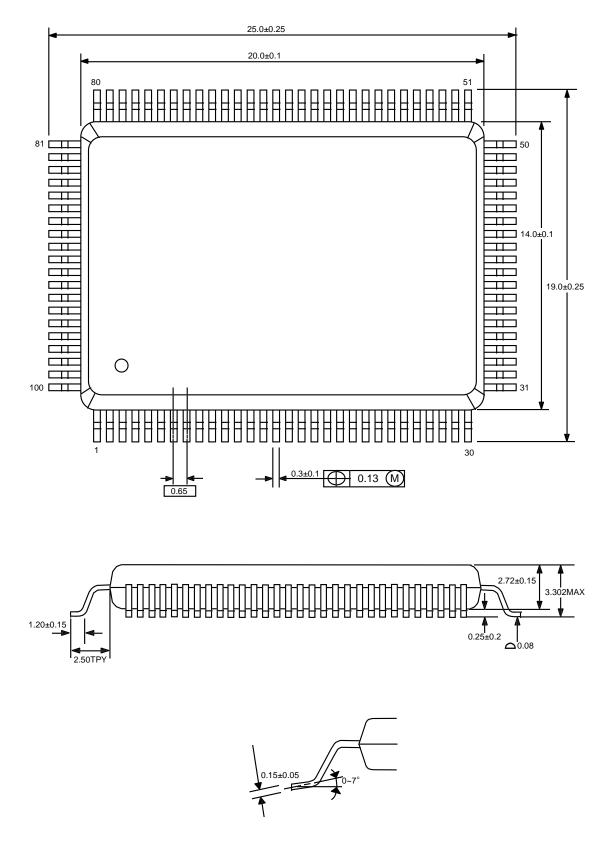

- \* 100 pin PQFP for VT82C587VP

#### **OVERVIEW**

The VT82C580VP *Apollo-VP* is a high performance, cost-effective and energy efficient chip set for the implementation of PCI/ISA desktop and notebook personal computer systems based on the 64-bit P54C/Pentium/K5/M1 super-scalar processors. CPU and cache interface is supported up to 66Mhz CPU external bus speed (with CPU internal speed up to 200Mhz and above). The CPU, DRAM and PCI bus are all independently powered so that each of the bus can be run at 3.3v or 5v, independently. The ISA bus always runs at 5v.

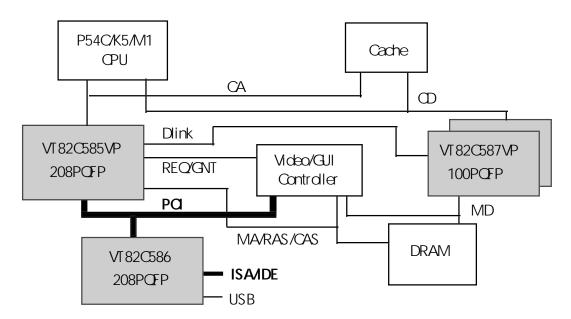

The VT82C580VP chip set consists of the VT82C585VP system controller, the VT82C586 PCI to ISA bridge, and two instances of the VT82C587VP data buffers. The CPU bus is minimally loaded with only the CPU, secondary cache and the chip set. The VT82C587VP data buffers isolate the CPU bus from the DRAM and PCI bus so that CPU and cache operation may run reliably at the high frequencies demanded by today's processors. The VT82C585VP contains arbitration logic to support the UMA (unified memory architecture) with video/GUI products from major video vendors. Multiple deep FIFOs (thirty-two double words) are included between multiple data paths to allow efficient concurrent operation and DRAM utilization. The VT82C586 PCI to ISA bridge includes integrated 206-style IPC (DMA, interrupt controller and timer), integrated keyboard controller with PS2 mouse support, integrated DS12885 style real time clock with extended 128 byte CMOS RAM, integrated master mode enhanced IDE controller with full scatter and gather capability, and integrated USB (universal serial bus) interface with root hub and two function ports with built-in physical layer transceiver. A complete main board can be implemented with only six TTLs. Please refer to Figure 1 for the system block diagram.

Figure 1. Apollo-VP System Block Diagram

The secondary (L2) cache is based on Burst Synchronous (Pipelined or non-pipelined) SRAM, asynchronous SRAM or cache module from 128KB to 2MB. For burst synchronous SRAMs, 3-1-1-1 timing can be achieved for both read and write transactions at 66Mhz. Four cache lines (16 quadwords) of CPU/cache to DRAM write buffers with concurrent write-back capability are included in the VT82C587VP data buffer chips to speed up the cache read and write miss cycles. These buffers also minimizes DRAM utilization and allows minimum performance degradation due to unified memory architecture with the video/GUI controller.

The VT82C580VP supports six banks of DRAMs up to 512KB. The DRAM controller supports Standard Page Mode DRAM, EDO-DRAM, Burst EDO-DRAM and Synchronous DRAM in a flexible mixed/match

manner. The Burst-EDO and Synchronous DRAM allows zero wait state bursting between the DRAM and the VT82C587VP data buffers at 66Mhz. The six banks of DRAM are grouped into three pairs with an arbitrary mixture of 256K/512K/1M/2M/4M/8M/16MxN DRAMs. Each bank may be populated either 32bit or 64bit data width.

The VT82C580VP supports Unified Memory Architecture with standard video/GUI controller based on the VESA UMA handshake protocols. The VT82C580VP includes the arbitration logic with multi-level of priorities, synchronous or asynchronous interface, programmable but guaranteed grant latency. The chip set is also responsible for DRAM refresh, direct frame buffer access, frame buffer memory mapping and arbitration control. With the intelligent arbitration, multiple deep buffers to minimize latency sensitivity and DRAM utilization and zero wait state bursting capability of Burst-EDO and Synchronous DRAMs, the UMA of the VT82C580VP can utilize DRAM most efficiently and deliver good performance for shared frame buffer applications.

The VT82C580VP supports the shadowing of the system, video and other BIOS to speed up the access. The video and system BIOS can also be write-protected and made cacheable. Access cycles to either E, D or C segment can be programmed to be an on-board EPROM cycle to allow the combination of system and video BIOS for an all-in-one system board implementation. The VT82C580VP can also be programmed to recognize write cycles as EPROM cycles to support field upgradability of flash EPROM BIOS.

The VT82C580VP supports 3.3/5v 32-bit PCI bus with 64-bit to 32-bit data conversion. Five levels (doublewords) of post write buffers are included to allow for concurrent CPU and PCI operation. Consecutive CPU addresses are converted into burst PCI cycles with byte merging capability for optimal CPU to PCI throughput. A 16-bit fast data link is established between the two VT82C587VP data units and the VT82C585VP so that the address, data and command information for CPU to PCI bus transactions is contained in the same chip. This arrangement, unique to the VT82C580VP chip set is crucial in achieving zero wait state buffer movement and implementing sophisticated and upgradable buffer management schemes such as the byte merging. For PCI master operation, Sixty-four levels (doublewords) of post write buffers and thirty two levels (doublewords) of prefetch buffers are included for concurrent PCI bus and DRAM/cache accesses. The chipset also supports enhanced PCI bus commands such as Memory-Read-Line, Memory-Read-Multiple and Memory-Write-Invalid commands to minimize snoop overhead. In addition, the chipset supports advanced features such as snoop ahead, snoop filtering, L1 write-back forward to PCI master and L1 write-back merged with PCI post write buffers to minimize PCI master read latency and DRAM utilization. The VT82C586 PCI to ISA bridge supports four levels (doublewords) of line buffers, type F DMA transfers and delay transaction to allow efficient PCI bus utilization and (PCI-2.1 compliant).

The integrated master mode IDE controller supports a dual channel/four device enhanced IDE bus with sixteen levels of double-word prefetch and write buffers. The data bus, control signals, write buffers and prefetch buffers are separated from those of the PCI bus so that performance and electrical loading are optimized. The command and recovery time of each IDE device can be individually programmed in units of PCI bus clock to achieve optimal speed of the device up to >22MB/s. Other features of the IDE controller include interlaced dual channel commands, full scatter and gather capability, bus master programming interface for ATA controllers SFF-8038 compliant and complete software driver support.

The VT82C580VP provides two plug and play ports for converting non plug and play devices into plug and play devices on the main board. The configuration mechanism is compliant with the plug and play BIOS and the Microsoft Windows 95<sup>™</sup> operating system.

The integrated power management unit offers the following modes: normal, doze, sleep, suspend and conserve. To determine the power management mode, the power management unit monitors IO events, interrupt, DMA and PCI master request signals to detect the status of system activity. Each event can be turned off or assigned to one of two event classes tracked by an idle timers, a peripheral timer and a general purpose timer. The system management interrupt (SMI) may be triggered by multiple sources including time-out of individual timers, occurrence of system activities, external input and software programming for flexible applications. Clock throttling, IO and power control are functions performed by the SMI routine. The power management unit is APM 1.1 compliant.

The VT82C580VP is ideal for high performance, high quality, high energy efficient and high integration desktop and notebook PCI/ISA computer systems.

# Configuration Register of VT82C580VP

#### VT82C585VP

All registers are located in the PCI configuration space. They should be programmed using PCI configuration mechanism 1 through CF8/CFC.

| <b>Offset</b> 1,0 | <b>Function</b><br>Vendor ID = 1106h (read only)                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3,2               | Device $ID = 0585h$ (read only)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 5,2               | Command register<br>bit 0: IO space = 1 (read only)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                   | <pre>bit 1: memory space = 1 (read only)<br/>bit 2: bus master = 1 (read only)<br/>bit 3: special cycle monitoring = 0 (read only)<br/>bit 4: memory write and invalid command = 0 (read only)<br/>bit 5: VGA palette snoop = 0 (read only)<br/>bit 6: parity error response (read/write, default=0)<br/>bit 7: address/data stepping = 0 (read only)<br/>bit 8: SERR# enable (read/write, default=0)<br/>bit 9: fast back-to-back cycle enable (read/write, default=0)<br/>bit 15-10: reserved</pre> |  |

| 7,6               | Status register (or IDX06<15:0>)<br>bit 0-6: reserved<br>bit 7: fast back-to-back: reserved<br>bit 8: data parity detected: reserved<br>bit 9-10: DEVSEL# timing: reserved<br>bit 11: signalled target abort: reserved<br>bit 12: received target abort (read only, write one to clear)<br>bit 13: signalled master abort: reserved<br>bit 14: signalled system error: reserved<br>bit 15: detected parity error (write only, write one to clear)                                                     |  |

| 08                | Revision I.D. $= 00h$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 09                | Program Interface = 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 0a                | Sub class code = 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0b                | Class code = 06h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 0c                | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 0d                | Latency Timer Default = 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| bit 2:0: | reserved                     |

|----------|------------------------------|

| bit 7-3: | guarantee time slice for CPU |

| 0e    | Header Type     | Default = 00 |

|-------|-----------------|--------------|

| Of    | BIST(Read Only) |              |

| 10-3f | Reserved        |              |

#### **Cache Control**

| 50 |          | Cache G    | Control R     | Register 1         | Default = 00                             |

|----|----------|------------|---------------|--------------------|------------------------------------------|

|    | bit 7-6: | Cache l    | Enable        |                    |                                          |

|    |          | Bit 7      | Bit6          |                    |                                          |

|    |          | 0          | 0             | - Cache disable    |                                          |

|    |          | 0          | 1             | - Cache Init       | - always does L2 fill                    |

|    |          | 1          | 0             | - Cache enable (   | normal operation)                        |

|    |          | 1          | 1             | - Reserved         | -                                        |

|    | bit 5:   | Enable/D   | Disable L     | inear Busrt (1/0)  |                                          |

|    | bit 4-3: | Tag Con    | figuratio     | n                  |                                          |

|    |          |            | Bit 3         |                    |                                          |

|    |          | 0          | 0             | - 8 Tags, no alt   |                                          |

|    |          | 0          | 1             | - 7 Tags, alt      |                                          |

|    |          | 1          | 0             | - 8 Tags, alt      |                                          |

|    |          | 1          | 1             | - 10 Tags, alt     |                                          |

|    | bit 2:   | BWE/GV     | WE BSR        | AM Interface is u  | sed Enable/Disable (1/0)                 |

|    | bit 1-0: |            |               |                    | MT<1:0>                                  |

|    |          | Bit 1      | Bit 0         |                    |                                          |

|    |          | 0          | 0             | - No SRAM          |                                          |

|    |          | 0          | 1             | - Async SRAM       |                                          |

|    |          | 1          | 0             | - Burst SRAM       |                                          |

|    |          | 1          | 1             | - Pipeline Burst   | SRAM                                     |

|    |          |            |               |                    |                                          |

| 51 |          |            |               | Register 2         | Default = 00                             |

|    | bit 7:   |            |               | wait state         |                                          |

|    |          |            | /S (3-x-x     |                    |                                          |

|    |          |            | S (4-x-x-     |                    |                                          |

|    | bit 6:   |            | rst wait s    |                    |                                          |

|    |          |            | S (x-2-2-     |                    |                                          |

|    |          |            | S (x-3-3-     |                    |                                          |

|    |          |            |               |                    | RAM only. The Sync. SRAM will always run |

|    |          |            |               | h read-hit and wri |                                          |

|    | bit 5:   |            |               |                    | Enable/Disable (1/0)                     |

|    | 1 . 4    | -          | -             | e read fill        |                                          |

|    | bit 4:   | Reserved   |               |                    |                                          |

|    | bit 3:   | SRAM E     |               |                    |                                          |

|    |          | 0:1Ba      |               |                    |                                          |

|    | 1.:4 0.  | 1:2 Ba     |               |                    |                                          |

|    | bit 2:   | Reserve    |               |                    |                                          |

|    | bit 1-0: | Cache S    |               |                    |                                          |

|    |          | Bit 1<br>0 | Bit 0<br>0    | 256V               |                                          |

|    |          | 0          |               | 256K               |                                          |

|    |          | 1          | $\frac{1}{0}$ | 512K<br>1M         |                                          |

|    |          | 1          | U             | 11111              |                                          |

|    |          |            |               |                    |                                          |

1 1 2M

| 52          | bit 7:<br>bit 6:<br>bit 5:<br>bit 4:<br>bit 3:<br>bit 2:<br>bit 1:<br>bit 0: | C0000-1<br>D0000-1<br>E0000-1<br>F0000-1<br>Allow V<br>Enable 2<br>L1 Writ<br>1 : wri<br>L2 Writ<br>1 : writ<br>1 : writ | C7FFF<br>DFFFF<br>FFFFF (<br>FFFFF (<br>Vrite-pr<br>L2 fill e<br>te Back/<br>te-back<br>te-back | Control<br>Cachable<br>Cachable/<br>Cachable/<br>Otect cach<br>ven CAC<br>Write-Th | e/Write-Pr<br>/Write-Pr<br>/Write-Pr<br>hed into 1<br>2HE is ina<br>ru | Protect<br>Protect<br>Protect<br>L1                                           |

|-------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 53          | bit 7:<br>bit 6:<br>bit 5:<br>bit 4:<br>bit 3:<br>bit 2-0:                   | Cache r<br>Write p<br>Dram p                                                                                             | ound W<br>ead pipe<br>ipeline c<br>ipeline c<br>ster Pee                                        | cycle Ena<br>cycle Ena                                                             | e Enable,<br>ble/Disal<br>ble/Disal                                    | le (1/0)<br>/Disable (1/0)<br>ble (1/0)                                       |

| 54-         | -55<br>bit 15-3:<br>bit 2-0:                                                 |                                                                                                                          |                                                                                                 | Region #<br>A<28:16<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1<br>0<br>1              |                                                                        | Default = 00                                                                  |

| 56-         | -57                                                                          | Non-Ca                                                                                                                   | achable                                                                                         | Region #                                                                           | 2                                                                      | Default = 00                                                                  |

| DRAM Contro | bl                                                                           |                                                                                                                          |                                                                                                 |                                                                                    |                                                                        |                                                                               |

| 58          | bit 7-5:<br>bit 4:<br>bit3-1:<br>bit 0:                                      | Bank 0/<br>Bit 7<br>0<br>0<br>0<br>0<br>1<br>Reserve                                                                     | Bit 6<br>0<br>1<br>1<br>x<br>cd<br>'3 MA M                                                      | uration<br>Map Type<br>Bit5<br>0<br>1<br>0<br>1<br>x<br>X<br>Map Type              | 8-bit<br>9-bit<br>10-bit<br>11-bit (<br>reserve                        | Default = 40<br>(note : 11-bit/12-bit has same decoding)<br>(see ma map)<br>d |

| 59 |          | DRA    | M Confi | guration | Default = 05 |

|----|----------|--------|---------|----------|--------------|

|    | bit 7-5: | Bank   | 4/5 MA  | Мар Тур  | be           |

|    | bit 4-3: | Reserv | ved     |          |              |

|    | bit 2-0: | Last B | ank Dra | am popul | ated         |

|    |          | Bit 2  | Bit 1   | Bit0     |              |

|    |          | 0      | 0       | 0        | bank 0       |

|    |          | 0      | 0       | 1        | bank 1       |

|    |          | 0      | 1       | 0        | bank 2       |

|    |          | 0      | 1       | 1        | bank 3       |

|    |          | 1      | 0       | 0        | bank 4       |

|    |          | 1      | 0       | 1        | bank 5       |

|    |          | 1      | 1       | Х        | reserved     |

|    |          |        |         |          |              |

5a-5f >>> DRAM ROW ENDING ADDRESS <<<

| 5a | Bank0 ending (CA[29:22]) | Default = 01 |

|----|--------------------------|--------------|

| 5b | Bank1 ending (CA[29:22]) | Default = 01 |

| 5c | Bank2 ending (CA[29:22]) | Default = 01 |

| 5d | Bank3 ending (CA[29:22]) | Default = 01 |

| 5e | Bank4 ending (CA[29:22]) | Default = 01 |

| 5f | Bank5 ending (CA[29:22]) | Default = 01 |

note : BIOS is required to fill ending for all banks even no memory is populated. The bank ending has to be in the incremental order

| 60 |          | DRAM Type     | Default = 00                                                                                  |

|----|----------|---------------|-----------------------------------------------------------------------------------------------|

|    |          | Reserved      |                                                                                               |

|    | bit 5-4: | DRAM type fo  | r Bank 4/5                                                                                    |

|    |          | Bit 5 Bit 4   |                                                                                               |

|    |          | 0 0           | Fast Page Mode                                                                                |

|    |          | 0 1           | EDO                                                                                           |

|    |          | 1 0           | Burst EDO                                                                                     |

|    |          | 1 1           | SDRAM                                                                                         |

|    | bit 3-2: | DRAM type fo  | r Bank 2/3                                                                                    |

|    | bit 1-0: | DRAM type for | r Bank 0/1                                                                                    |

| 61 | bit 7-6: |               | Control - C0000-CFFFF Default = 00<br>Fh<br>read/write disable<br>write enable<br>read enable |

|    |          | 1 0           |                                                                                               |

|    |          | 1 1           | read/write enable                                                                             |

|    | bit 5-4: | C8000H-CBFF   | ìFh                                                                                           |

|    | bit 3-2: | C4000h-C7FFI  | Fh                                                                                            |

| 62 | bit 7-6:<br>bit 5-4:<br>bit 3-2:<br>bit 1-0: | Shadow RAM Control - D0000-DFFFF Default = 00<br>DC000h-DFFFFh<br>D8000H-DBFFFh<br>D4000h-D7FFFh<br>D0000H-D3FFFh                                                                                        |

|----|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63 | bit 7-6:<br>bit 5-4:<br>bit 3-2:<br>bit 1:   | Shadow RAM Control - E0000-FFFFDefault = 00E0000h-EFFFFhF0000h-FFFFFhMemory HolesBit 3Bit 20001512K-640K10115M-16M (1M)11114M-16M (2M)SMI redirect to a0000h-bfffh Enable/Disable (1/0)                  |

|    | bit 0:                                       | Enable/Disable a0000h-bffffh read/write to DRAM (1/0)                                                                                                                                                    |

| 64 | bit 7-6:                                     | DRAM TimingDefault = ABRAS precharge timeBit 7Bit 60002T0110                                                                                                                                             |

|    | bit 5-4:                                     | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    |

|    | bit 3-2:<br>bit 1:                           | CAS pulse width         Bit 3       Bit 2         0       0       1T         0       1       2T         1       0       3T         1       1       4T         Write pulse width       Verter pulse width |

|    |                                              | 0 1T                                                                                                                                                                                                     |

|    | bit 0:                                       | 1 2T<br>RAS to CAS delay<br>0 2T<br>1 3T<br>note : Must set to 1 for FPG or EDO DRAM for 60 or 66Mhz                                                                                                     |

| 65 | bit 7-6:                                     | DRAM Control Default = 00<br>Dram page mode control<br>Bit 7 Bit 6                                                                                                                                       |

|    |                                              | 00Page close after each access01reserved10Page stays open after access11Page close, if next pipeline access pending is offpage                                                                           |

|    | bit 5:                                       | Fast DRAM decoding Enable/Disable (1/0)                                                                                                                                                                  |

|    | bit 4:   | Reduce DRAM leadoff cycle by 1T Enable/Disable (1/0)<br>note : this option is only allowed for BEDO and EDO |

|----|----------|-------------------------------------------------------------------------------------------------------------|

|    | bit 3:   | Reserved                                                                                                    |

|    | bit 2:   | 32-bit DRAM control use TA9 Enable/Disable (1/0) (PLINK0 Strapping)                                         |

|    | bit 1:   | Fast EDO/BEDO access Enable/Disable (1/0) (1 En 110 Strupping)                                              |

|    | UIT 1.   | Note: for 50Mhz bus speed only                                                                              |

|    | bit 0:   | Delay DRAM read cycle 1T when Write-Buffer is not empty Enable/Disable                                      |

|    |          | (1/0)                                                                                                       |

| 66 |          | BEDO/EDO Control Default = 00                                                                               |

|    | bit 7:   | EDO test mode Enable/Disable (1/0)                                                                          |

|    | bit 6:   | BEDO programming mode Enable/Disable (1/0)                                                                  |

|    | bit 5:   | BEDO cycle latency Enable/Disable (1/0)                                                                     |

|    | bit 4-3: | Reserved                                                                                                    |

|    | bit 2:   | 1ws for MD to CD pop Enable/Disable (1/0)                                                                   |

|    | bit 1:   | Reduce BEDO RAS precharge time by 1T Enable/Disable(1/0)                                                    |

|    | bit 0:   | BEDO RAS to CAS Delay at 2T Enable/Disable(1/0)                                                             |

|    | on 0.    | note: This bit overwrites RX64 bit 0 for BEDO                                                               |

|    |          | note. This bit overwrites KA04 bit 0 for BEDO                                                               |

| 67 |          | 32-bit DRAM width                                                                                           |

|    | bit 7-6: | Reserved                                                                                                    |

|    | bit 5:   | Bank 5 width : 1: 32-bit, 0 : 64 bit                                                                        |

|    | bit 4:   | Bank 4 width : 1: 32-bit, 0 : 64 bit                                                                        |

|    | bit 3:   | Bank 3 width : 1: 32-bit, 0 : 64 bit                                                                        |

|    | bit 2:   | Bank 2 width : 1: 32-bit, 0 : 64 bit                                                                        |

|    | bit 1:   | Bank 1 width : 1: 32-bit, 0 : 64 bit                                                                        |

|    | bit 0:   | Bank 0 width : 1: 32-bit, 0 : 64 bit                                                                        |

| 60 |          |                                                                                                             |

| 68 | 1.14.7   | UMA Control Register 1 Default = $00$                                                                       |

|    | bit 7:   | Arbitration Mechanism                                                                                       |

|    |          | 0 - 2-pin                                                                                                   |

|    |          | 1 - 3-pin                                                                                                   |

|    | bit 6:   | Arbitration Synchronous                                                                                     |

|    |          | 0 - Synchronous                                                                                             |

|    |          | 1 - Asynchronous                                                                                            |

|    | bit 5:   | Enable/Disable direct frame-buffer access (1/0) <b>LFBAC</b>                                                |

|    |          | * LFBAC=1 will direct cpu access in [LFBA,LFBA+UFBSZ-1]                                                     |

|    |          | range to last dram bank defined in LSTBK[2:0]                                                               |

|    | bit 4:   | Enable/Disable Unified Frame Buffer (1/0) UFBON                                                             |

|    |          | * UFBON will forward cpu access in [ENDxA,ENDxA-UFBSZ] to pci                                               |

|    | bit 3:   | Reserved                                                                                                    |

|    | bit 2:   | RAS# driven active after MGNT# deassertion                                                                  |

|    |          | 0 1T                                                                                                        |

|    |          | 1 2T                                                                                                        |

|    | bit 1:   | MREQ1 polarity                                                                                              |

|    | UIT 1.   |                                                                                                             |

|    |          | 0 active low                                                                                                |

|    | 1.4.0    | 1 active high                                                                                               |

|    | bit 0:   | Invert A22 for 12MB DRAM                                                                                    |

|    |          | 0 : not inverted                                                                                            |

|    |          | 1 : inverted                                                                                                |

| 69 |          | UMA Control Register 2 Default = 00                                                                         |

|    | hit 7 3. | Frame huffer hase for direct access CA[31:27]                                                               |

bit 7-3: Frame buffer base for direct access, CA[31:27]

|    |                | Bit 2 Bit 1 Bit0                                                                                                                         |

|----|----------------|------------------------------------------------------------------------------------------------------------------------------------------|

|    |                | 0 0 0 512K                                                                                                                               |

|    |                | 0 	 0 	 1 	 1M                                                                                                                           |

|    |                | 0 1 0 1.5M                                                                                                                               |

|    |                | 0 	 1 	 1 	 2M                                                                                                                           |

|    |                | 1 	 0 	 0 	 2.5M                                                                                                                         |

|    |                | 1 	 0 	 1 	 3M                                                                                                                           |

|    |                | 1 1 0 3.5M                                                                                                                               |

|    |                | 1 1 1 4M                                                                                                                                 |

| 6a |                | Refresh Control Default = 00                                                                                                             |

|    | bit 7-0:       |                                                                                                                                          |

|    |                | note: When set to 00, DRAM refresh is diable                                                                                             |

|    |                |                                                                                                                                          |

| 6b |                | Misc. Default = 00                                                                                                                       |

|    | bit 7:         | CBR( CAS-before-RAS) refresh Enable/Disable(1/0)                                                                                         |

|    | bit 6:         | Burst Refresh (burst 4 times) Enable/Disable (1/0)                                                                                       |

|    | bit 5-0:       | Reserved                                                                                                                                 |

|    |                |                                                                                                                                          |

| 6c | 1.4.7          | SDRAM control (revision I.D. $\geq 10$ )                                                                                                 |

|    | bit 7:         | Reserved                                                                                                                                 |

|    | bit 6:         | SDRAM burst write                                                                                                                        |

|    | bit 5:         | MA11 bank interleave enable                                                                                                              |

|    | bit 4:         | SDRAM turbo mode                                                                                                                         |

|    | 1.4.2          | allow continuous burst at 1-1-1-1 rate                                                                                                   |

|    | bit 3:         | SDRAM CAS latency                                                                                                                        |

|    |                | 1 : cycle latency is 2                                                                                                                   |

|    | h:+ 2 0.       | 0 : cycle latency is 3                                                                                                                   |

|    | bit 2-0:       | SDRAM operation Mode select                                                                                                              |

|    | 000 :<br>001 : | Normal SDRAM mode (default)<br>NOP command enable.                                                                                       |

|    |                |                                                                                                                                          |

|    | 010 :          | All Banks Precharge command enable.                                                                                                      |

|    | 011:           | CPU to DRAM cycles are converted to all banks precharge command<br>CPU to DRAM cycle converted to commands, the command is driven        |

|    | 011.           | CPU to DRAM cycle converted to commands, the command is driven<br>on MA[11:0]. The BIOS selects an appropriate host address for each row |

|    |                | of memory such that the right commands are generated on MA[11:0]                                                                         |

|    | 100 :          | CBR Cycle enable                                                                                                                         |

|    |                | lx : reserved                                                                                                                            |

|    | 101/11         |                                                                                                                                          |

| 6d |                | DRAM control drive strength (revision I.D. $\geq$ 10)                                                                                    |

|    | bit 7:         | bank decoding test                                                                                                                       |

|    | bit 6:         | RAS precharge 2T when DRAM bank switch                                                                                                   |

|    | bit 5:         | CAS precharge 2T for DRAM burst write                                                                                                    |

|    | bit 4:         | Force SMM mode                                                                                                                           |

|    | bit 3:         | SDRAM control drive (0/1 : 12/24ma)                                                                                                      |

|    | bit 2:         | MA/WE drive (0/1 : 12/24ma)                                                                                                              |

- bit 2: MA/WE drive (0/1 : 12/24ma)

- bit 1: CAS drive (0/1 : 8/12ma)

- bit 0: RAS drive (0/1 : 12/24)

6e-6f Reserved

#### **PCI Bus Control**

| 70 |          | PCI Buffer Control Default = 00                                         |

|----|----------|-------------------------------------------------------------------------|

|    | bit 7:   | CPU to PCI post-write Enable/Disable (1/0)                              |

|    | bit 6:   | PCI master to DRAM post-write Enable/Disable (1/0)                      |

|    | bit 5:   | PCI master to DRAM prefetch Enable/Disable (1/0)                        |

|    | bit 4-1: | Reserved (all 0)                                                        |

|    | bit 0:   | Delay transaction optimization Enable/Disable (0/1)                     |

| 71 |          | CPU to PCI flow control 1 Default = 00                                  |

|    | bit 7:   | Dynamic burst Enable/Disable (1/0)                                      |

|    | bit 6:   | Byte merge Enable/Disable (1/0)                                         |

|    | bit 5:   | Reserved (all 0)                                                        |

|    | bit 4:   | PCI IO cycle post write Enable/Disable (1/0)                            |

|    | bit 3:   | PCI burst Enable/Disable (1/0)                                          |

|    |          | bit7=1 will override this option                                        |

|    | bit 2:   | PCI side fast back to back write Enable/Disable (1/0)                   |

|    | bit 1:   | Quick frame generation Enable/Disable (1/0)                             |

|    | bit 0:   | 1 wait state pci cycle Enable/Disable (1/0)                             |

|    |          |                                                                         |

| 72 |          | CPU to PCI flow control 2 Default = 00                                  |

|    | bit 7:   | Retry status over 16/64 times                                           |

|    |          | 0 - No retry occurred                                                   |

|    |          | 1 - retry occurred (write 1 to clear)                                   |

|    | bit 6:   | Retry timeout action                                                    |

|    |          | 0 - no action taken except record status                                |

|    |          | (retry forever)                                                         |

|    |          | 1 - take action to flush buffer or                                      |

|    |          | return FFFFFFF for read                                                 |

|    | bit 5-4: | Retry control                                                           |

|    |          | Bit 5 Bit 4                                                             |

|    |          | 0 0 retry 2 times, back off CPU                                         |

|    |          | 0 1 retry 16 times                                                      |

|    |          | 1 0 retry 4 times, back off CPU                                         |

|    | 1:0      | 1 1 retry 64 times                                                      |

|    | bit 3:   | When the data is posting and retry fail, pop the failed data out, and   |

|    | 1:40     | keep posting if there is any, Enable/Disable (1/0).                     |

|    | bit 2:   | Backoff CPU when read data from pci and retry fail Enable/Disable (1/0) |

|    | bit 1-0: | Reserved                                                                |

| 73 |          | PCI master control 1 Default = 00                                       |

|    | bit 7:   | Local memory decoding                                                   |

|    |          | 0 - fast (address phase)                                                |

|    |          | 1 - medium (1st data phase)                                             |

|    | bit 6:   | PCI master 1 wait state write                                           |

|    |          | 0 - Zero wait state TRDY                                                |

|    |          | 1 - One wait state TRDY response                                        |

|    | bit 5:   | PCI master 1 wait state read                                            |

|    |          | 0 - Zero wait state TRDY response                                       |

|    |          | 1 - One wait state TRDY response                                        |

|    | bit 4:   | Reserved (all 0)                                                        |

|    | bit 3:   | Assert STOP after PCI master write timeout Enable/Disable (1/0)         |

|    | bit 2:   | Assert STOP after PCI master read timeout Enable/Disable (1/0)          |

|    | bit 1:   | LOCK function Enable/Disable (1/0)                                      |

- bit 1:LOCK function Enable/Disable (1/0)bit 0:PCI master broken timer enable

- -14-

Force into arbitration when there is no FRAME 16 PCICLK after the GRANT.

| 74 | bit 7:<br>bit 6:<br>bit 5-0: | PCI master control 2<br>PCI Enhance command support En<br>PCI master single write merge Ena<br>Reserved |                                         |            |            |                                              |  |  |  |

|----|------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------|------------|------------|----------------------------------------------|--|--|--|

| 75 |                              | PCI art                                                                                                 | oitration                               |            |            | Default = 00                                 |  |  |  |

|    | bit 7:                       | Arbitrat                                                                                                | tion Mecl                               | hanism     |            |                                              |  |  |  |

|    |                              |                                                                                                         | I has prio                              |            |            |                                              |  |  |  |

|    |                              | 1 - Fai                                                                                                 | r arbitrat                              | ion betw   | een pci a  | and cpu                                      |  |  |  |

|    | bit 6:                       |                                                                                                         | tion Mod                                | -          |            |                                              |  |  |  |

|    |                              |                                                                                                         | Q-based                                 | •          |            | 0                                            |  |  |  |

|    |                              |                                                                                                         |                                         | d (arbitra | ite at end | l of each FRAME)                             |  |  |  |

|    |                              | Reserve                                                                                                 |                                         |            |            |                                              |  |  |  |

|    | bit 3-0:                     |                                                                                                         |                                         |            |            | to arbitration after certain period of time) |  |  |  |

|    |                              | Bit 3                                                                                                   | Bit 2                                   | Bit 1      | Bit 0      |                                              |  |  |  |

|    |                              | 0                                                                                                       | 0                                       | 0          | 0          | disable                                      |  |  |  |

|    |                              | 0                                                                                                       | 0                                       | 0          | 1          | 1x32 PCICLK                                  |  |  |  |

|    |                              | 0                                                                                                       | 0                                       | 1          | 0          | 2x32 PCICLK                                  |  |  |  |

|    |                              | 1                                                                                                       | 1                                       | <br>1      | 1          | 15x32 PCICLK                                 |  |  |  |

|    |                              |                                                                                                         |                                         |            |            |                                              |  |  |  |

| 76 |                              | Extensi                                                                                                 | ion (revis                              | sion I.D.  | ≥ 10)      | Default = 00                                 |  |  |  |

|    | bit 7:                       | CPU ar                                                                                                  | CPU arbitration mode                    |            |            |                                              |  |  |  |

|    |                              | 0 - CP                                                                                                  | 0 - CPU is granted between 3 PCI master |            |            |                                              |  |  |  |

|    |                              | 1 - CP                                                                                                  | U is gran                               | ted betw   | een 2 PC   | CI master                                    |  |  |  |

|    | bit 6:                       | Reserve                                                                                                 | ed                                      |            |            |                                              |  |  |  |

|    | bit 5-4:                     | CPU fa                                                                                                  | ir arbitrat                             | tion in FI | RAME#      | based arbitration (revision I.D. $\geq 10$ ) |  |  |  |

|    |                              | 00 - di                                                                                                 | sable                                   |            |            |                                              |  |  |  |

|    |                              | 01 - ev                                                                                                 | very 1 PC                               | I master   | will gran  | nt to CPU                                    |  |  |  |

|    |                              | 10 - ev                                                                                                 | very 2 PC                               | I master   | will gran  | nt to CPU                                    |  |  |  |

|    |                              | 11 - ev                                                                                                 | very 3 PC                               | I master   | will gran  | nt to CPU                                    |  |  |  |

|    | bit 3-1:                     |                                                                                                         | ed (all 0)                              |            |            |                                              |  |  |  |

|    | bit 0:                       |                                                                                                         | the conf                                |            |            |                                              |  |  |  |

|    |                              | 0 - M                                                                                                   | echanism                                | 1 #1, use  | CF8/CF0    | C                                            |  |  |  |

1 - Mechanism #2, use C0xx

#### VT82C586

All registers are located in the PCI configuration space. They should be programmed using PCI configuration mechanism 1 through CF8/CFC.

| <b>Offset</b> 1,0                                                                              | <b>Function</b><br>Vendor ID = $1106h$ (read only)                                                                                                                                                                                                                                                              |

|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3,2                                                                                            | Device ID = 0586h (read only)                                                                                                                                                                                                                                                                                   |

| 5,4<br>bit 15<br>bit 3:<br>bit 2:<br>bit 1:<br>bit 0:                                          | Command register<br>-4: reserved<br>special cycle enable<br>bus master = 1 (read only)<br>memory space = 1 (read only)<br>IO space = 1 (read only)                                                                                                                                                              |

| 7,6<br>bit 15<br>bit 14<br>bit 13<br>bit 12<br>bit 11<br>bit 10<br>bit 8:<br>bit 7:<br>bit 6-0 | <ul> <li>signalled system error (read only)</li> <li>signalled master abort (read only)</li> <li>received target abort (read only, write one to clear)</li> <li>signalled target abort: reserved</li> <li>-9: DEVSEL# timing: fixed to 01 data parity detected: reserved fast back-to-back: reserved</li> </ul> |

| 08                                                                                             | Revision I.D. = 00h                                                                                                                                                                                                                                                                                             |

| 09                                                                                             | Program Interface = 00h                                                                                                                                                                                                                                                                                         |

| 0a                                                                                             | Sub class code = 01h                                                                                                                                                                                                                                                                                            |

| 0b                                                                                             | Class code = 06h                                                                                                                                                                                                                                                                                                |

| 0c                                                                                             | Reserved                                                                                                                                                                                                                                                                                                        |

| 0d                                                                                             | Reserved                                                                                                                                                                                                                                                                                                        |

| 0e                                                                                             | Header Type - Multifunction device (Read only) Default = 80                                                                                                                                                                                                                                                     |

| Of                                                                                             | BIST(Read Only)                                                                                                                                                                                                                                                                                                 |

| ISA Bus Control                                                                                |                                                                                                                                                                                                                                                                                                                 |

| 40 |        | ISA bus control         | Default = 00     |

|----|--------|-------------------------|------------------|

|    | bit 7: | Extra/normal ISA com    | mand delay (1/0) |

|    | bit 6: | Enable/disable SRDY     | delay (1/0)      |

|    | bit 5: | 5/4 ISA slave wait stat | te (1/0)         |

|    | bit 4: | 4/2 chip-set IO wait st | ate (1/0)        |

|    | bit 3: | Enable/disable I/O rec  | overy time (1/0) |

|    | bit 2: | Enable/disable extended | -ALE (1/0)       |

- bit 1: 0/1 ROM wait state (1/0)

- bit 0: Enable/disable ROM write (1/0)

- 41 Refresh and Port 92 Default = 00

- bit 7: Disable/enable bus refresh arbitration (1/0)

- bit 6: Reserved

- bit 5: Enable/disable Port 92 fast reset (1/0)

- bit 4: Reserved

- bit 3: Enable/disable double DMA clock (1/0)

- bit 2: Reserved

- bit 1: Enable/disable refresh request test mode (1/0)

- bit 0: Reserved

42

#### ISA clock control/Misc. Default = 00

- bit 7: Disable/enable latch IO16# (1/0)

- bit 6: Enable/disable MS16 output (1/0)

- bit 5: Enable/disable master request test mode (1/0)

- bit 4: Enable/disable turbo pin (1/0)

- bit 3: Enable/disable ISA CLOCK from the following selections (1/0) if disable, ISA CLOCK = PCICLK/4

- bit 2-0: AT BUS CLOCK select

| - | 11 DO | JCLOC |       |           |

|---|-------|-------|-------|-----------|

|   | Bit 2 | Bit 1 | Bit 0 |           |

|   | 0     | 0     | 0     | PCICLK/3  |

|   | 0     | 0     | 1     | PCICLK/2  |

|   | 0     | 1     | 0     | PCICLK/4  |

|   | 0     | 1     | 1     | PCICLK/6  |

|   | 1     | 0     | 0     | PCICLK/5  |

|   | 1     | 0     | 1     | PCICLK/10 |

|   | 1     | 1     | 0     | PCICLK/12 |

|   | 1     | 1     | 1     | OSC/2     |

|   |       |       |       |           |

Note: Procedure for ISA CLOCK switching

1. Set bit 3 to 0

- 2. Change value of bit 2-0

- 3. Set bit 3 to 1

| 43 | bit 7-6:  | ROM decoding control<br>Reserved    | Default = 00                     |

|----|-----------|-------------------------------------|----------------------------------|

|    | bit 5:    | 10001100                            | MCS decode Enable/Disable (1/0)  |

|    | bit $4$ : |                                     | MCS decode Enable/Disable (1/0)  |

|    | bit 3:    |                                     | DMCS decode Enable/Disable (1/0) |

|    | bit 2:    |                                     | OMCS decode Enable/Disable (1/0) |

|    | bit 1:    |                                     | MCS decode Enable/Disable (1/0)  |

|    | bit 0:    |                                     | OMCS decode Enable/Disable (1/0) |

| 44 |           | Keyboard Controller control         | Default = 00                     |

|    | bit 7-3:  | Reserved ( for internal test only ) |                                  |

|    | bit 2:    | RKBLOCK                             |                                  |

|    | bit 1:    | A0EN disable/enable PS2 mouse       | :                                |

|    | bit 0:    | Reserved                            |                                  |

| 45 |           | Type F DMA control                  | Default = 00                     |

|    | bit 7:<br>bit 6:<br>bit 5:<br>bit 4:<br>bit 3:<br>bit 2:<br>bit 1:<br>bit 0: | Enable/disable ISA Master/DMA to PCI line buffer (1/0)<br>Enable/Disable DMA type F timing on channel 7 (1/0)<br>Enable/Disable DMA type F timing on channel 6 (1/0)<br>Enable/Disable DMA type F timing on channel 5 (1/0)<br>Enable/Disable DMA type F timing on channel 3 (1/0)<br>Enable/Disable DMA type F timing on channel 2 (1/0)<br>Enable/Disable DMA type F timing on channel 1 (1/0)<br>Enable/Disable DMA type F timing on channel 1 (1/0)                                                                                                     |